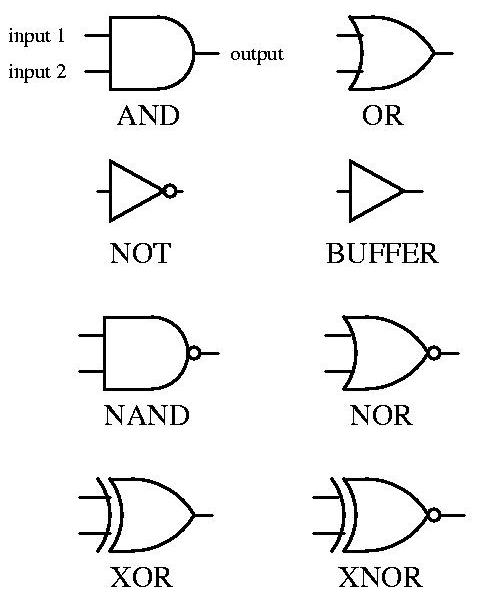

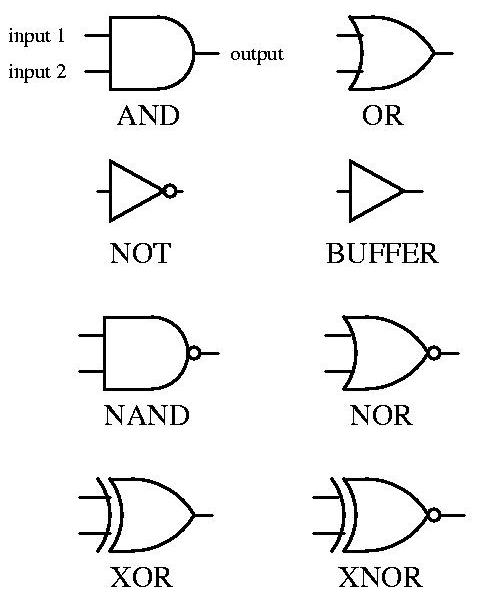

この図を見ると、NAND ゲートは AND ゲートの出力のところに小さい丸をつけ た形で表されている。この丸は否定を表している。x NAND y は x ∧ y の否 定だったことを思い出してほしい。NOR, XNOR ゲートについても同様である。 NOT ゲートもバッファの出力に否定を入れたものと考えられるので、バッファ の記号の出力に丸をつけたものになっている。 入力に丸をつけることもある。例えば、x NAND y = ¬(x ∧ y) = ¬x ∨ ¬y なので、下図で「=」で結んだ2つの回路は論理的に同等になる。

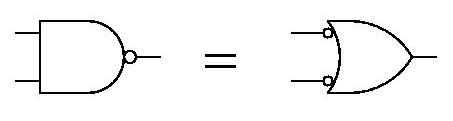

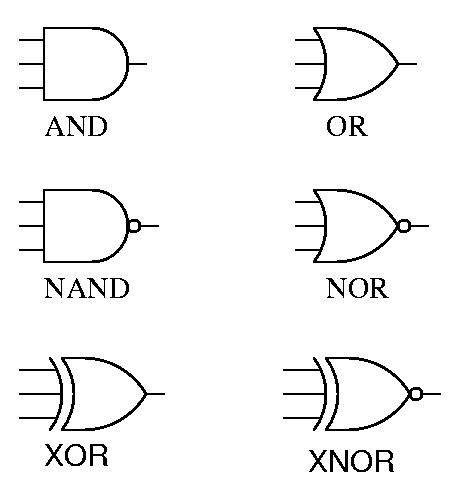

入力が3本あったり、4本あったりするものもよく使われている。(そういう回 路が入った IC を売っている。) 3入力については、以下の図のようになる(4 入力も同様)。

3入力の AND や OR の動作は、ご想像の通り、 (x ∧ y ∧ z) と (x ∨ y ∨ z) で表され、 NAND や NOR についても単にこれらの否定である。 3入力XOR についても (x XOR y XOR z) になっており、XNOR はその否定である。

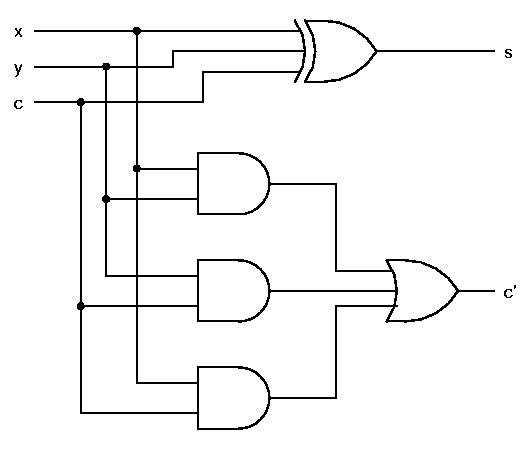

下図により、1ビット全加算器の動作を確かめることができる。 ただし、今の所このソフトウェアには3入力ゲートがないので、 3入力 XOR ゲートの代りに2入力 XOR ゲートを2つ組合せて使っている。 3入力 OR についても同様。

このような組合せ論理回路を設計するには、例えば次のようにすればよい:

ただし、論理和標準形は大きな式になりがちなので、必ずしもこのような方法が良いとは言えない。

次へ